# NB2AS Description

The NB2AS is a microcontroller development system that is compatible with the Arduino/Sanguino software environment. For system development a variety of peripherals are available.

### Features

- Replaceable and upgradeable CPU

- Compatible with the Arduino/Sanguino development tools

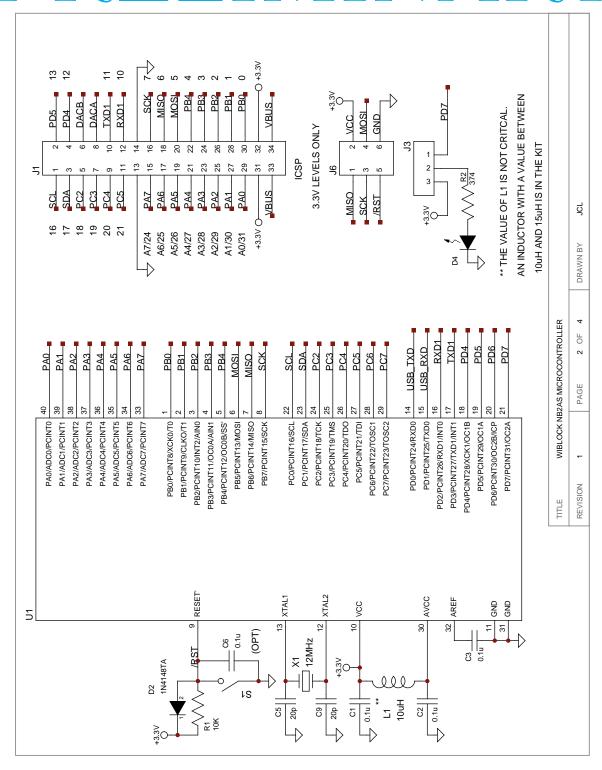

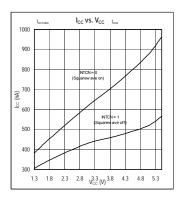

- ATmega644P running at 12MHz with a  $V_{CC}$  of 3.3V.

- SMD land patterns designed for hand assembly.

- 3.55" x 2.15" (Fits in the larger Altoids tin)

- Atmega I/O connections, DAC outputs and RTC interrupt output lines are wired to a single 34 pin header. Application boards can be mounted parallel using vertical connectors, co-planar using right-angle connectors or remotely using a cable.

- microSD Card

- Series MOSFET enables power to be cycled on the uSD card. This enables the uSD to be properly reset.

- Card-detect output wired to an I/O line.

- Tested with Transcend 1GB, Sandisk 2GB and Sandisk 4GB HC.

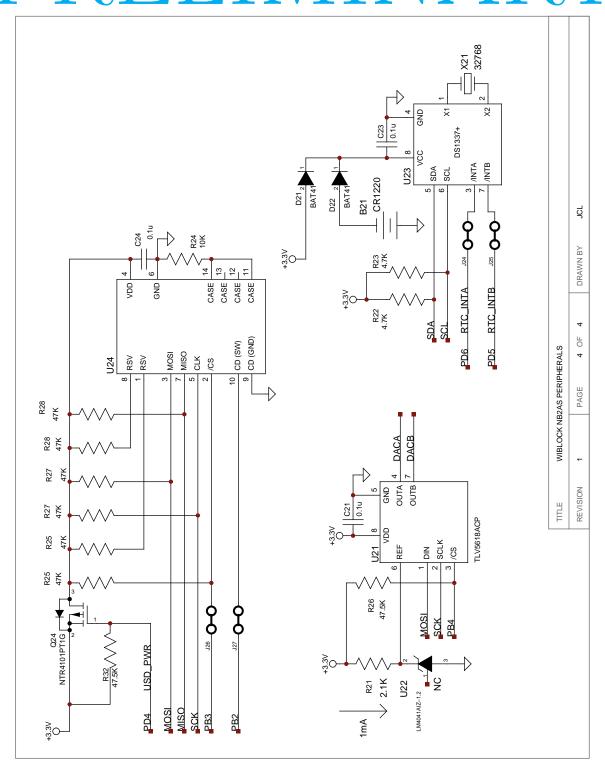

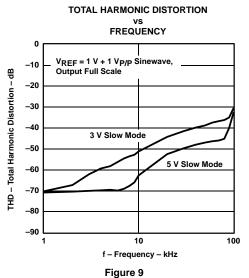

- DAC Features

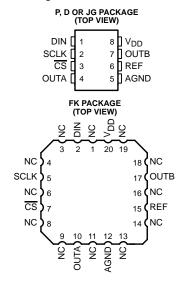

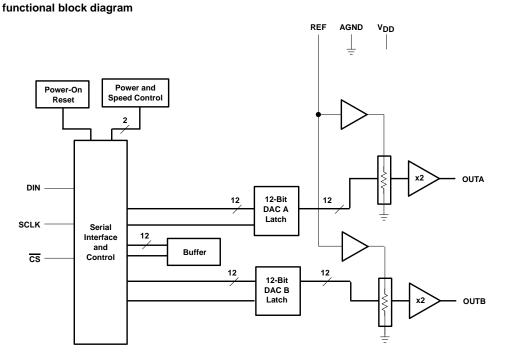

- Two channels, twelve bits per channel, SPI interface.

- Reference 1.225 V,  $\pm 0.1\%$  (initial accuracy), 100 ppm per °C maximum drift,

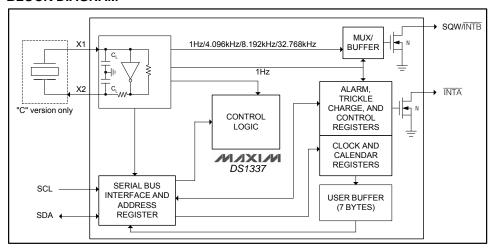

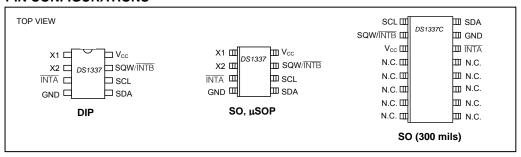

#### • RTC Features

- Real-Time Clock (RTC) counts Seconds, Minutes, Hours, Day, Date, Month, and Year with Leap-Year Compensation Valid Up to 2100

- Two Time-of-Day Alarms

- Programmable Square-Wave Output

- Backup power from a CR1220 coin cell.

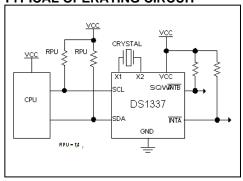

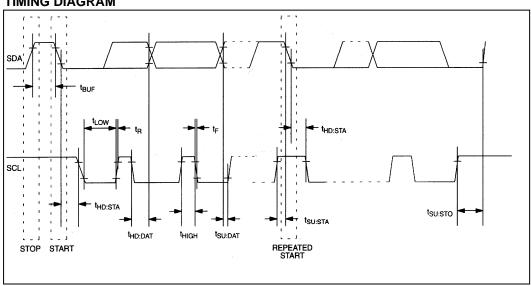

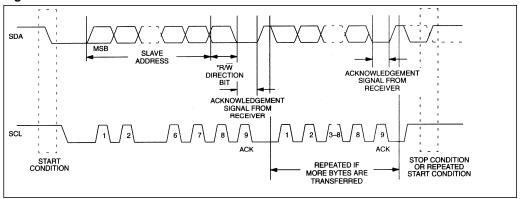

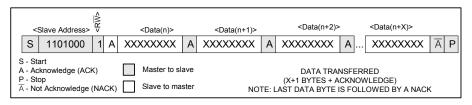

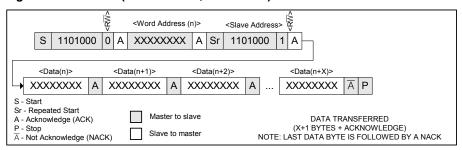

- I<sup>2</sup>C Serial Interface

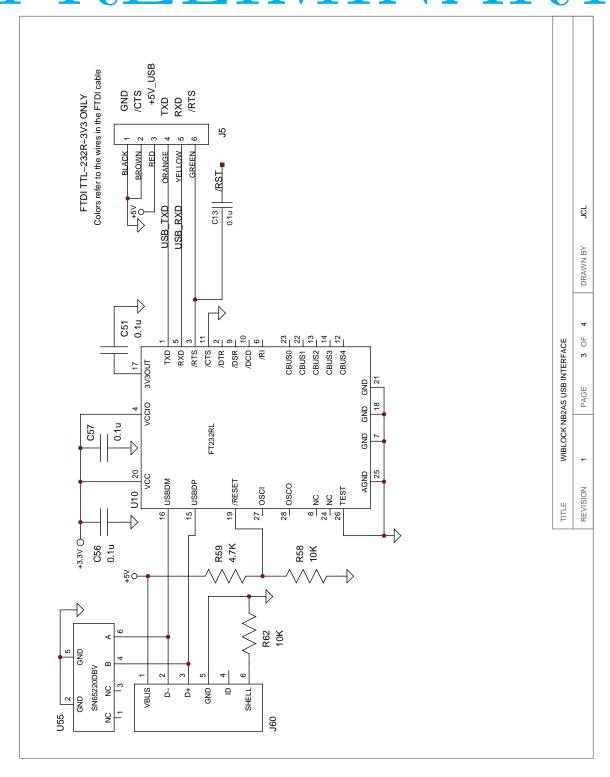

- The board can be built with either a USB interface or with a six pin header for use with an USB to serial cable. The USB interface circuitry includes transient suppression.

- ICSP port (3.3V levels)

- A/D reference supply filtered per Atmel specification.

- Reset circuit per Atmel specification.

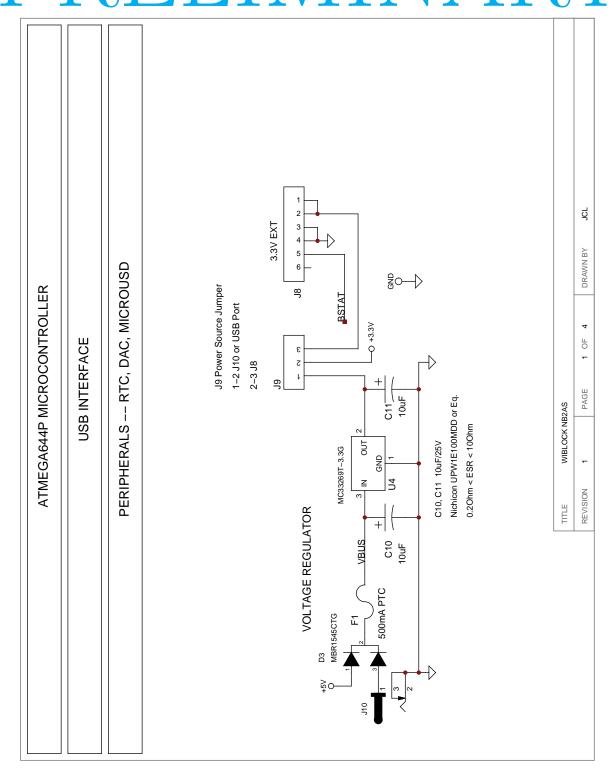

- Power supply is jumpered between either an LDO or an external 3.3V supply. The LDO input is diode or'ed from a wall adapter or the USB 5V supply.

- The NB2AS accessories include an Li-ion charger, prototyping board and a terminal block interface.

# 1 Assembling the NB2AS

Semiconductors are electrostatic-sensitive devices. Proper ESD handling precautions need to be taken to avoid damage.

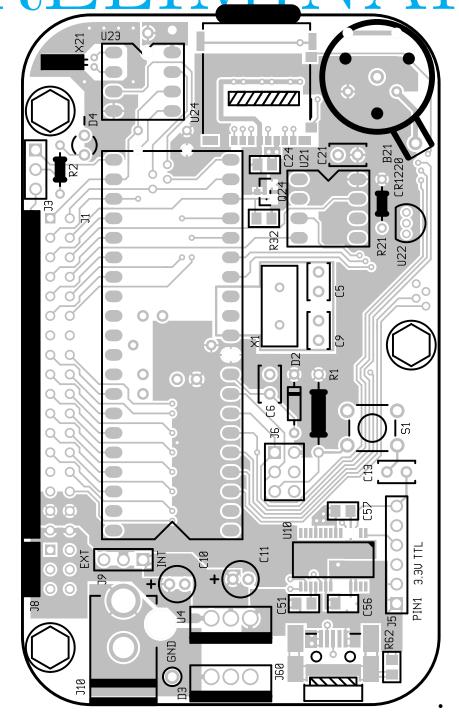

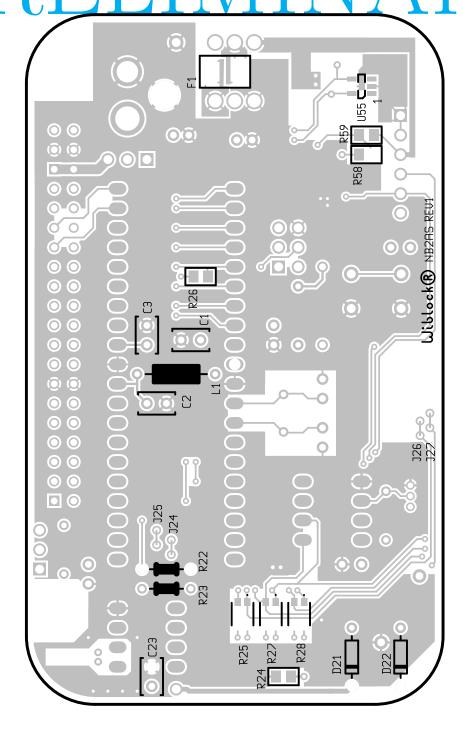

The Bill of Materials (BOM) and Component List are in section 7. For full page assembly drawings see Figure 1 (top) and Figure 2 (bottom).

Extra care needs to be taken when soldering the right-angle connector(s) – J1 and J8 (opt). The outer edge of the connector bodies should not protrude over the edge of the board. After soldering and the connector pins should be parallel to the board.

A DC source with current limiting is useful for testing each section of the NB2AS as you build it.

All of the headers supplied with the kit are breakaway headers. The single row headers, J3 (3x1), J5 (6x1), J9 (3x1) may come as individual headers or as strips that need to be broken. Most kits will contain either two 6x1 headers or one 12x1. Break these headers to create J3, J5 and J9.

If you are not building the USB circuit proceed to subsection 1.4.

# 1.1 microSD Circuit Assembly (Top)

Solder the top side components:

- U24 (uSD socket)

- Q24

- C24

- R32

# 1.2 USB Circuit Assembly (Top)

Solder the top side components:

- J60

- U10 FT232RL

- C57, C56, C51

- R62

### 1.3 SMD Components (Bottom)

Solder the bottom side components:

- R25, R27, R28

- R24

- R26

- U55

- R58

- F1

At this point clean the flux off of the top and bottom side of the board. After the board is cleaned visually inspect the board for solder shorts, opens and cold solder joints.

# 1.4 Bottom Side Components

- C1, C2, C3

- L1

The value of inductor L1 is not critical. Kits will contain an inductor with a value between  $10\mu H$  and  $15\mu H$

- D21, D22

- C23

# 1.5 Power Supply Circuit Assembly

Solder the top side components:

• C10, C11

C10 and C11 are polarized parts. The long lead is the positive. The short lead is the negative. Make sure that the positive lead is inserted into positive hole in the PCB

• U4

Be careful to not mixup U4 and D3. U4 is marked MC33269T-3.3G Make sure that the tab is aligned to the tab marking on the PCB.

• D3

Be careful to not mixup D3 and U4. D3 is marked MBR1545CTG Make sure that the tab is aligned to the tab marking on the PCB.

- J9

- J10

- J8 (optional)

J8 enables the usage of an external 3.3V power source with the NB2AS. If you do not need this function then you can omit the installation of J8. J8 is not included in the kit.

At this point clean the flux off of the top and bottom side of the board. After the board is cleaned visually inspect the board for solder shorts, opens and cold solder joints.

### 1.5.1 Testing the Power Supply Circuit

If possible apply power through J10 with a current limited +5V supply. The current drawn from the +5V supply should not exceed a few milliamperes. If it does then verify the orientation on C10, C11, D3, U4.

### 1.6 Microcontroller Circuit Assembly

Solder the top side components:

• R1

The tolerance of R1 is not critical. The 1% resistor has five color bands (brown, black, black, red, brown)

• D2

Line the cathode marking on D1 with the cathode marking on the silkscreen

• C13, C6 (optional).

C6 is optional and is not included in the kit. It is meant for applications that require additional filtering of the reset line. Applications that use USB download or ISP programmers like the AVRISPMKII will not require additional filtering. Also, the reset function that uses the /RTS line from the USB interface will not function with C6 installed.

• D4

The negative lead of the LED is the short lead. Align the short lead with the negative marking on the PCB.

• R2

The tolerance of R2 is not critical. The 1% resistor has five color bands (red, red, brown, black, brown).

- J3

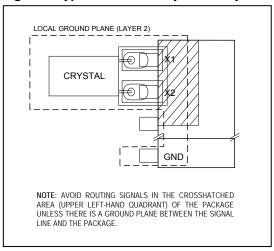

- X1, C5, C9

- U1 (socket)

- J6

- J1

J1 that is included with the NB2AS Kit are right angle connectors. If your application requires parallel board mounting or a cable connection then replace J1 with vertical headers. A 2x17 receptacle can also be used.

• J4 (optional).

At this point clean the flux off of the top and bottom side of the board. After the board is cleaned visually inspect the board for solder shorts, opens and cold solder joints. After inserting an ATmega644P into the U1 socket the microcontroller section of the NB2AS should be fully functional. If possibly apply power through J10 with a current limited  $+5\mathrm{V}$  supply. The current drawn should not exceed  $10\mathrm{mA}$  (20mA if the J3 jumper is installed in the VCC position).

# 1.7 RTC Circuit Assembly

R22 and R23 are the  $I^2C$  pullups. The value included in the NB2A kit is 4.7K $\Omega$ . If you are running the  $I^2C$  bus at lower frequencies you could increase the value of these resistors. If your application has external pullups you should remove these resistors (See subsection 5.1).

The DS1337 interrupt lines, /INTA and /INTB are jumpered to PD6 (Sanguion pin ??) and PD5 (Sanguion pin ??) respectively. To disconnect /INTA cut jumper J24. To disconnect /INTB cut jumper J25 (See subsection 5.2).

• R22, R23

The tolerance of R22 and R23 is not critical. Some kits include a 5% resistor others include a 1% resistor. The 5% resistor has four color bands (yellow, violet, red, gold). The 1% resistor has five color bands (yellow, violet, black, brown, brown).

- B21 battery holder

- X21 crystal

If you are assembling a revision one PCB then see ??.

- U23 socket

# 1.8 DAC Circuit Assembly

- R21

- U22

- C21

- U21 socket

# 1.9 Electro-mechanical Components

The electro-mechanical components are sensitive to washing. Place all of these last and lightly wash afterward. If water does get into these components let them dry out before applying power.

Solder the top side components:

• S1

# 1.10 Mounting Hardware

Space has been provided for three #2 hex standoffs and washers.

### 1.11 IC Installation and Test

Remove each IC from the antistatic foam and insert it into the appropriate socket aligning the notch in the IC package with notch mark indicated on the PCB silkscreen. Be careful to align pins on both sides of the socket prior to pressing the IC into the socket.

- ATmega644P (U1)

- TLV5618 (U21)

- DS1337 (U32)

The board is now ready to program. To test the programming using the Arduino/Sanguino tools (see ??).

| J1   | 17x2 header | I/O connections from the AT-mega644P. See Table 2                                                                     |

|------|-------------|-----------------------------------------------------------------------------------------------------------------------|

| 13   | 3x1 header  | Jumper to switch the debug LED between 3.3V (right position) and ATmega644P pin PD7 (left position) (Sanguino pin 15) |

| J5   | 6x1 header  | USB header for an FTDI TTL-232R-3V3 cable. This is only installed if the USB circuit is not populated.                |

| J6   | 3x2 header  | ICSP header                                                                                                           |

| Ј8   | 3x2 header  | External 3.3V regulated voltage input. See Table 3                                                                    |

| J9   | 3x1 jumper  | Jumper to switch between the external 3.3V input and the on board LDO.                                                |

| J10  | 2.1mm Jack  | 5V to 15V unregulated DC. The power dissipation in U4 needs to be kept below one watt.                                |

| .160 | USB Mini-B  |                                                                                                                       |

Table 1: NB2AS connectors

| N   | NB2AS                         | ATr         | nega644P | Sanguino |  |

|-----|-------------------------------|-------------|----------|----------|--|

| Pin | Function                      | Pin         | Function | Pin      |  |

| 1   | PCO/SCL                       | 22          | PCO/SCL  | D16      |  |

| 2   | PD5                           | 19          | PD5      | D13      |  |

| 3   | PC1/SDA                       | 23 PC1/SDA  |          | D17      |  |

| 4   | PD4                           | 18          | PD4      | D12      |  |

| 5   | PC2                           | 24          | PC2      | D18      |  |

| 6   | DACB                          |             |          |          |  |

| 7   | PC3                           | 25          | PC3      | D19      |  |

| 8   | DACA                          |             |          |          |  |

| 9   | PC4                           | 26          | PC4      | D20      |  |

| 10  | PD3/TXD1                      | 17          | PD3/TXD1 | D11      |  |

| 11  | PC5                           | 27          | PC5      | D21      |  |

| 12  | PD2/RXD1                      | 16          | PD2/RXD1 | D10      |  |

| 13  | GND                           | 31          | GND      |          |  |

| 14  | GND                           | 31          | GND      |          |  |

| 15  | PA7/ADC7                      | 33          | PA7/ADC7 | A7/D24   |  |

| 16  | PB7/SCK                       | 8           | PB7/SCK  | D7       |  |

| 17  | 17   PA6/ADC6   34   PA6/ADC6 |             | PA6/ADC6 | A6/D25   |  |

| 18  | PB6/MISO                      | 7 PB6/MISC  |          | D6       |  |

| 19  | PA5/ADC5                      | 35          | PA5/ADC5 | A5/D26   |  |

| 20  | PB5/MOSI                      | 6 PB5/MOSI  |          | D5       |  |

| 21  | PA4/ADC4                      | 36 PA4/ADC4 |          | A4/D27   |  |

| 22  | PB4                           | 5           | PB4      | D4       |  |

| 23  | PA3/ADC3                      | 37          | PA3/ADC3 | A3/D28   |  |

| 24  | PB3                           | 4           | PB3      | D3       |  |

| 25  | PA2/ADC2                      | 38          | PA2/ADC2 | A2/D29   |  |

| 26  | PB2                           | 3           | PB2      | D2       |  |

| 27  | PA1/ADC1                      | 39          | PA1/ADC1 | A1/D30   |  |

| 28  | PB1                           | 2           | PB1      | D1       |  |

| 29  | PAO/ADCO                      | 40          | PAO/ADCO | AO/D31   |  |

| 30  | PB0                           | 1           | PB0      | DO       |  |

| 31  | 3.3V                          |             |          |          |  |

| 32  | 3.3V                          |             |          |          |  |

| 33  | VBUS                          |             |          |          |  |

| 34  | VBUS                          |             |          |          |  |

Table 2: J1 Pinout

# 2.2 J8 Header

| Pin | Function |

|-----|----------|

| 1   | 3.3V EXT |

| 2   | 3.3V EXT |

| 3   | GND      |

| 4   | GND      |

| 5   | BSTAT    |

| 6   | NC       |

Table 3: J8 Pinout

# 3.1 Power Supply

The NB2AS can be powered by a wall adapter, the USB port or an external regulated 3.3V supply. The wall adapter and the USB port are diode or'ed and are connected to the input of a LDO regulator (U4). Jumper J9 selects between the two power sources – INT is the LDO regulator (U4), EXT is the power source connected to J8.

Power Jumper in the Internal Position

Power Jumper in the External Position

It is critical to keep the power dissipation in the LDO regulator (U4), to less than one watt. The voltage drop across U4 is

$$V_{drop} = V_{in} - 0.5V - 3.3V$$

where  $V_{in}$  is the greater of the wall adapter voltage or +5V (USB 5V supply). The power dissipated in U4 is given by

$$P_{diss} = V_{drop} \cdot I_{system}$$

where  $I_{system}$  is the load of the NB2AS plus its peripheral circuitry.

# 3.2 Powering from the USB Port

The intial startup load of a device connected to the USB port must not exceed  $10\mu F$  in parallel with  $44\Omega$  (USB-IF, 2000a). Peripheral circuitry attached to the NB2AS may produce a system load that exceeds the specification.

### 3.3 $V_{BUS}$

$V_{BUS}$  is the unregulated voltage at the cathode of the or'ing diode (D3). Applications that require current beyond the current rating of the LDO regulator (U4) should use  $V_{BUS}$ . Since the only voltage drop between the input power source and  $V_{BUS}$  is the  $V_F$  of the or'ing diode (D3) it is more efficient to use  $V_{BUS}$  rather than the  $+3.3\mathrm{V}$  supply as an input voltage for other power conversions.

The debug LED, D4, can be connected to the +3.3V supply or to U1 pin 21 (PD7) of the ATmega644P. U1 pin 21

corresponds to Sanguino pin "15".

LED jumper in the VCC position

LED jumper in the PD7 position

# 4 Programming the NB2AS

The NB2AS can be programmed using the Arduino tools (version 0011 or more recent) with the Sanguino extensions (See Sanguino Hints) using the USB interface from a PC or MAC. If you purchased a board with a USB interface than connect a USB Mini-B cable to J60. If you purchased a board with an FTDI header then connect the FTDI receptacle to J5 matching pin one of the cable to the pin one marking on the board.

# 4.1 Selecting the proper board

In order for the Arduino tools to recoginze a new board the boards.txt file needs to be modified. As part of the Sanguino tools installation the Sanguino parameters where added to the boards.txt file.

An easy way to add entries for the NB2AS is to copy the Sanguino entries and make the following changes to the copied lines -

- 1. Change all occurances of Sanguino to nb2as

- 2. Change the name to NB2AS (Line 1)

- 3. Change the maximum\_size to 61440 (Line 3)

- 4. Change the f\_cpu to 12000000L (Line 13)

- 5. Change the core to nb2as (Line 14)

- 6. Change the high\_fuses to 0xDA (Line 6)

The modified lines are shown in Listing 1 (with annotations).

Listing 1: Modifications to the boards.txt file for the NB2AS

- nb2as.**name=**NB2AS

- $_2$  nb2as.upload.protocol=stk500

- 3 nb2as.upload.maximum\_size=61440

- $_4$  nb2as.upload.speed=38400

$_{5}~\mathrm{nb2as.bootloader.low\_fuses} = 0\mathrm{xFF}$

6 nb2as.bootloader.high\_fuses=0xDA

7 nb2as.bootloader.extended\_fuses=0xFD

$_8$  nb2as. **bootloader**. **path**=atmega644p

9 nb2as.bootloader.file=ATmegaBOOT\_644P.hex

nb2as.**bootloader**.unlock\_bits=0x3F

nb2as.**bootloader**.lock\_bits=0x0F

nb2as. **build**.mcu=atmega644p

nb2as. **build**.  $\mathbf{f_cpu} = 12000000$ L

nb2as.build.core=nb2as

nb2as.verbose=false

With a modified boards.txt select nb2as from the Tools->Board menu.

# 4.2 Downloading a program to the NB2AS

The NB2AS must be rebooted to start program download. This can be done by pressing the reset button S1 immediately before starting the download. If your USB port is configured to set RTS on close then the reset will occur automatically.

### 4.3 Downloading a bootloader

The NB2AS is powered from 3.3V. Any device that connects to the NB2AS needs to output 3.3V TTL levels. The Atmel AVRATAVRISPMKII and Ladyada USBtiny are compatible with the NB2AS.

To use the Ladyada USBtiny remove the USBtiny jumper, JP3, and plug the USBtiny cable into the NB2AS ICSP header. With JP3 removed the USBtiny output buffer (IC2) is powered by the  $V_{cc}$  from the NB2AS (3.3V). The USBtiny output buffer (IC2) is a 74AHC125 which will tolerate 5V levels when powered from a 3.3V supply.

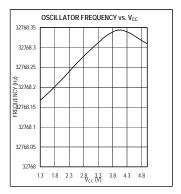

# 5 Real-Time Clock

The NB2AS real-time clock (RTC) consists of a DS1337 that is powered by a CR1220 coin cell. Communication to the DS1337 is through the I<sup>2</sup>C interface (a.k.a. two-wire or TWI). The I<sup>2</sup>C pullup resistors on the NB2AS are  $4.7 \mathrm{K}\Omega$ . The interrupt lines, /INTA and /INTB are jumpered to PD6 (Sanguino pin 6) and PD5 (Sanguino pin 5) respectively. There are no pullup resistors on the interrupt lines. If external pullups are not added then the internal pullups of the ATmega644P need to be used.

Programming the RTC requires a software library for the DS1337 and for the TWI interface. Both of these libraries are available for download at wiblocks.

### 5.1 I<sup>2</sup>C Pullup Resistors

The maximum bus capacitance of the I<sup>2</sup>C bus is 400pF. Unless a large number of devices are on the bus or devices are connected using long cables an NB2AS system will not get

close to this limit. The DS1337 represents a maximum load of 10pF.

The mimunum pullup resistance is 966  $\Omega$  (  $\frac{V_{CC}-0.4V}{3mA}). The maximum value pullup resistance is$

$$R_{pullup(max)} = \begin{cases} \frac{1000 \text{nS}}{C_{BUS}} & \text{if } F_{SCL} \leq 100 \text{kHz}, \\ \\ \frac{300 \text{nS}}{C_{BUS}} & \text{if } 100 \text{kHz} < F_{SCL} \leq 400 \text{kHz}. \end{cases}$$

where  $C_{BUS}$  is the maximum bus capacitance, , and  $V_{CC}$  is 3.3V for the NB2AS.

With a 100pF load (10 times the DS1337 load), the maximum resistance for 400kHz operation is  $3K\Omega$ . For 100kHz the maximum resistance is  $10K\Omega$ . If only the DS1337 is on the I<sup>2</sup>C bus the maximum resistances would be  $100K\Omega$  (100kHz) and  $30K\Omega$  (400kHz). The minimum resistance, which is not dependent on bus capacitance, is  $966\Omega$  for any operating frequency and  $C_{BUS}$ . (Atmel, 2009a)

### 5.2 DS1337 Interrupt Lines

The DS1337 interrupt lines, /INTA and /INTB are jumpered to PD6 (Sanguino pin 6) and PD5 (Sanguino pin 5) respectively. To disconnect /INTA cut jumper J24. To disconnect /INTB cut jumper J25.

There are no pullup resistors connected to the interrupt lines. To use the interrupt lines with the ATmega644P the internal pull-up resistors need to be enabled. For the ATmega644P  $20 \mathrm{K}\Omega \leq R_{pullup} \leq 50 \mathrm{K}\Omega$  which is sufficient to pullup the DS1337 lines. (Atmel, 2009b).

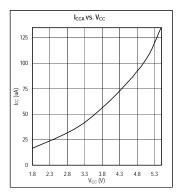

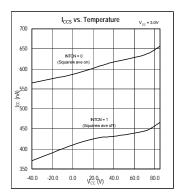

# 5.3 RTC Battery Life

The DS1337 operates with a  $V_{CC}$  from 1.8V to 5.5V. On the NB2AS the  $V_{CC}$  line is diode or'ed between the CR1220 coin cell and the 3.3V supply. The capacity of the CR1220 is 40mAH (to 2V). When the I2C bus is active the DS1337 is supplied from the 3.3V supply. When the device is inactive the DS1337 is in standby mode which has a maximum current is  $1.5\mu$ A.(Maxim, 2009a) The maximum battery life is  $\approx 26000$  hours.

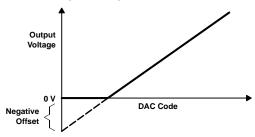

# 6 Dual DAC

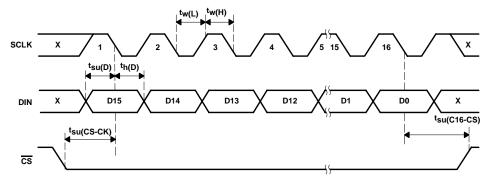

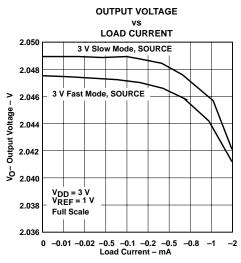

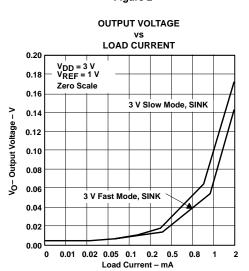

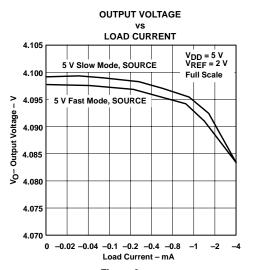

The dual DAC on the NB2AS is the Texas Instruments TLV5618 which has a resolution of 12 bits. Communication to the DAC is through the SPI interface. Data is shifted into the shift register. After 16bits of data is shifted or the /CS line rises the contents of the shift register is transferred to the target latches. The selection of the target latches is set by the control bits.

The reference used is the LM4041. The reference voltage is  $1.225\mathrm{V}, \pm 0.1\%$  (initial accuracy),  $100\mathrm{ppm}$  per °C maximum drift. Since the NB2AS is a  $3.3\mathrm{V}$  system the maximum reference voltage for the TLV5618 is  $1.8\mathrm{V}$ .

Atmel. (2009a). 8-bit AVR Microcontroller with 16/32/64K Bytes In-System Programmable Flash. 334. (Retrieved April 28, 2009, from http://www.atmel.com/dyn/resources/prod\_documents/doc8011.pdf)

Atmel. (2009b). 8-bit AVR Microcontroller with 16/32/64K Bytes In-System Programmable Flash. 326. (Retrieved April 28, 2009, from http://www.atmel.com/dyn/resources/prod\_documents/doc8011.pdf)

Atmel. (2009c). 8-bit AVR Microcontroller with 16/32/64K Bytes In-System Programmable Flash. (Retrieved April 28, 2009, from http://www.atmel.com/dyn/resources/prod\_documents/doc8011.pdf)

Maxim. (2009a, July). DS1337 I2C Serial Real-Time Clock. 2-3. (Retrieved September 30, 2009, from http://datasheets.maxim-ic.com/en/ds/DS1337-DS1337C.pdf)

Maxim. (2009b, July). DS1337 I2C Serial Real-Time Clock. (Retrieved September 30, 2009, from http://datasheets.maxim-ic.com/en/ds/DS1337-DS1337C.pdf)

USB-IF, I. (2000a, April 27). Universal Serial Bus Specification. 171-177.

USB-IF, I. (2000b, April 27). Universal Serial Bus Specification.

Table 4: Bill of Materials

Kit: NB2AS-KIT3

| B21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Qty | Reference       | Part Number                    | Description                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|--------------------------------|---------------------------------------------|

| C13, C21, C23 2 C5, C9 CAPR-20P0-100V-NPO-5T00 capacitor, ceramic, 20pF 2 C10, C11 CAPPR_Nichicon_UPW1E100MDD 4 C24, C51, C56, CAPC-0U1-50V-X7R-0805 capacitor, Nichicon UPW1E100MDD 5 C57 1 D2 DIOA-1N4148 diode, 1N4148 1 D3 DIO_On-Semi_MBR1545CTG diode, dual, On-Semi_MBR1545CTG 1 D4 LEDR-1T-GRN-2M00 LED, T1, Green diode, BAT41 1 F1 FUSE_Littelfuse_1812L050PR fuse, 0.5A 1812 1 J1 HDR_RA BR_17X2-100M header, RA, 17x2, 100mils header, 3x1, 100mils header, 3x1, 100mils header, 3x2, 100mils power jack, 2.1mm 1 J6 HDR_BR-3X2-100M header, 3x2, 100mils power jack, 2.1mm 1 J60 Molex_67503-1020 inductor, 10uH, 10% 1 Q24 FET_P_On-Semi_NTR4101PT1G FET_P, -20V, 3.2A resistor, 10K, 1/4W, 1% resistor, 14X (NW, 1% resistor, 2.1K, 1/8W, 1% resistor, 4.7K, 1/8W, 18W, 18C, 18C, 18C, 18C, 18C, 18C, 18C, 18C                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1   |                 |                                |                                             |

| C5, C9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7   | C1, C2, C3, C6, | CAPR-0U10-50V-X7R-100M         | capacitor, ceramic, 0.1uF, 10%, 50V, X7R    |

| C10, C11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | C13, C21, C23   |                                |                                             |

| 4         C24, C51, C56, C57         CAPC-0U1-50V-X7R-0805         capacitor, ceramic, 0.1uF, 16V, 0805           1         D2         DIOA-1N4148         diode, 1N4148           1         D3         DIO_On-Semi_MBR1545CTG         diode, dual, On-Semi_MBR1545CTG           1         D4         LEDR-1T-GRN-2M00         LED, T1, Green           2         D21, D22         DIOA-BAT41         diode, BAT41           1         FI         FUSE_Littlefluse_1812L050PR         fuse, 0.5A 1812           2         J3, J9         HDR_BR-3X1-100M         header, RA, 17x2, 100mils           1         J6         HDR_BR-3X2-100M         header, 3x1, 100mils           1         J60         Molex_67503-1020         mower jack, 2.1mm           1         J60         Molex_67503-1020         miductor, 10uH, 10%           1         FET_P_On-Semi_NTR4101PT1G         FET_P, -20V, 3.2A           1         R1         RES-10K0-0W25-1T00         resistor, 2.1K, 1/4W, 1%           2         R22, R23         RES-4K70-0W125-1T00         resistor, 2.1K, 1/8W, 1%           3         R24, R58, R62         RES-10K0-0805-1T00         resistor, 4.7K, 1/8W, 1/8           3         R25, R27, R28         RES-4K70-0W125-5T00-2N         resistor, 4.7K, 0805, 1%                                                                                                          | 2   | C5, C9          | CAPR-20P0-100V-NPO-5T00        | capacitor, ceramic, 20pF                    |

| C57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2   | C10, C11        | CAPPR_Nichicon_UPW1E100MDD     | capacitor, Nichicon UPW1E100MDD             |

| D2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4   | C24, C51, C56,  | CAPC-0U1-50V-X7R-0805          | capacitor, ceramic, 0.1uF, 16V, 0805        |

| D3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     | C57             |                                |                                             |

| 1         D4         LEDR-1T-GRN-2M00         LED, T1, Green diode, BAT41           2         D21, D22         DIOA-BAT41         diode, BAT41           1         F1         FUSE_Littelfuse_1812L050PR         fuse, 0.5A 1812           1         J1         HDR.RA_BR-17X2-100M         header, RA, 17x2, 100mils           2         J3, J9         HDR.BR-3X1-100M         header, 3x1, 100mils           1         J6         HDR.BR-3X2-100M         header, 3x2, 100mils           1         J10         CON_CUI-PJ-202AH         power jack, 2.1mm           1         J60         Molex_67503-1020         inductor, 10uH, 10%           1         L1         INDA-10UH-130M-10T0         inductor, 10uH, 10%           1         Q24         FET_P_On-Semi_NTR4101PT1G         FET, P, -20V, 3.2A           1         R1         RES-10K0-0W25-1T00         resistor, 10K, 1/4W, 1%           1         R2         RES-374R-0W125-1T00         resistor, 2.1K, 1/8W, 1%           2         R22, R23         RES-4K70-0W125-1T00         resistor, 4.7K, 1/8W, 1%           3         R24, R58, R62         RES-10K0-0W51-T00         resistor, 4.7K, 1/8W, 1%           3         R25, R27, R28         RESCAV-47K0-0W125-5T00-2N         resistor, 4.7K, 0805, 1% <tr< th=""><th>1</th><td>D2</td><td>DIOA-1N4148</td><td>diode, 1N4148</td></tr<>                              | 1   | D2              | DIOA-1N4148                    | diode, 1N4148                               |

| 1         D4         LEDR-1T-GRN-2M00         LED, T1, Green diode, BAT41           2         D21, D22         DIOA-BAT41         diode, BAT41           1         F1         FUSE_Littelfuse_1812L050PR         fuse, 0.5A 1812           1         J1         HDR.RA_BR-17X2-100M         header, RA, 17x2, 100mils           2         J3, J9         HDR.BR-3X1-100M         header, 3x1, 100mils           1         J6         HDR.BR-3X2-100M         header, 3x2, 100mils           1         J10         CON_CUI-PJ-202AH         power jack, 2.1mm           1         J60         Molex_67503-1020         inductor, 10uH, 10%           1         L1         INDA-10UH-130M-10T0         inductor, 10uH, 10%           1         Q24         FET_P_On-Semi_NTR4101PT1G         FET, P, -20V, 3.2A           1         R1         RES-10K0-0W25-1T00         resistor, 10K, 1/4W, 1%           1         R2         RES-374R-0W125-1T00         resistor, 2.1K, 1/8W, 1%           2         R22, R23         RES-4K70-0W125-1T00         resistor, 4.7K, 1/8W, 1%           3         R24, R58, R62         RES-10K0-0W51-T00         resistor, 4.7K, 1/8W, 1%           3         R25, R27, R28         RESCAV-47K0-0W125-5T00-2N         resistor, 4.7K, 0805, 1% <tr< th=""><th>1</th><td>D3</td><td>DIO_On-Semi_MBR1545CTG</td><td>diode, dual, On-Semi MBR1545CTG</td></tr<> | 1   | D3              | DIO_On-Semi_MBR1545CTG         | diode, dual, On-Semi MBR1545CTG             |

| 1         F1         FUSE_Littelfuse_1812L050PR         fuse, 0.5A 1812           1         J1         HDR_RA_BR-17X2-100M         header, RA, 17x2, 100mils           2         J3, J9         HDR_BR-3X1-100M         header, 3x1, 100mils           1         J6         HDR_BR-3X2-100M         header, 3x2, 100mils           1         J10         CON_CUI-PJ-202AH         power jack, 2.1mm           1         J60         Molex_67503-1020         inductor, 10uH, 10%           1         L1         INDA-10UH-130M-10T0         inductor, 10uH, 10%           1         Q24         FET_P_On-Semi_NTR4101PT1G         FET, P, -20V, 3.2A           1         R1         RES-10K0-0W25-1T00         resistor, 10K, 1/4W, 1%            1         R2         RES-374R-0W125-1T00         resistor, 2.1K, 1/8W, 1%           2         R22, R23         RES-4K70-0W125-1T00         resistor, 2.1K, 1/8W, 1%           3         R24, R58, R62         RES-10K0-0805-1T00         resistor, 10K, 0805. 1%           3         R25, R27, R28         RESCAV-47K0-0W125-5T00-2N         resistor, 47K, 1/8W, 1206x2 Concave           2         R26, R32         RES-4K70-0805-1T00         resistor, 47K, 0805, 1%           1         R59         RES-4K70-0805-1T00         resistor, 47K, 0                                                                                        | 1   | D4              | LEDR-1T-GRN-2M00               |                                             |

| 1         F1         FUSE_Littelfuse_1812L050PR         fuse, 0.5A 1812           1         J1         HDR_RA_BR-17X2-100M         header, RA, 17x2, 100mils           2         J3, J9         HDR_BR-3X1-100M         header, 3x1, 100mils           1         J6         HDR_BR-3X2-100M         header, 3x2, 100mils           1         J10         CON_CUI-PJ-202AH         power jack, 2.1mm           1         J60         Molex_67503-1020         inductor, 10uH, 10%           1         L1         INDA-10UH-130M-10T0         inductor, 10uH, 10%           1         Q24         FET_P_On-Semi_NTR4101PT1G         FET, P, -20V, 3.2A           1         R1         RES-10K0-0W25-1T00         resistor, 10K, 1/4W, 1%            1         R2         RES-374R-0W125-1T00         resistor, 2.1K, 1/8W, 1%           2         R22, R23         RES-4K70-0W125-1T00         resistor, 2.1K, 1/8W, 1%           3         R24, R58, R62         RES-10K0-0805-1T00         resistor, 10K, 0805. 1%           3         R25, R27, R28         RESCAV-47K0-0W125-5T00-2N         resistor, 47K, 1/8W, 1206x2 Concave           2         R26, R32         RES-4K70-0805-1T00         resistor, 47K, 0805, 1%           1         R59         RES-4K70-0805-1T00         resistor, 47K, 0                                                                                        | 2   | D21, D22        | DIOA-BAT41                     | diode, BAT41                                |

| 2 J3, J9 HDR_BR-3X1-100M header, 3x1, 100mils 1 J6 HDR_BR-3X2-100M header, 3x2, 100mils 1 J10 CON_CUI-PJ-202AH power jack, 2.1mm 1 J60 Molex_67503-1020 1 L1 INDA-10UH-130M-10T0 inductor, 10uH, 10% 1 Q24 FET_P_On-Semi_NTR4101PT1G FET, P, -20V, 3.2A 1 R1 RES-10K0-0W25-1T00 resistor, 10K, 1/4W, 1% 1 R2 RES-374R-0W125-1T00 resistor, 374 Ohm, 1/8W, 1% 1 R21 RES-2K10-0W125-1T00 resistor, 2.1K, 1/8W, 1% 2 R22, R23 RES-4K70-0W125-1T00 resistor, 4.7K, 1/8W, 1% 3 R24, R58, R62 RES-10K0-0805-1T00 resistor, 10K, 0805. 1% 3 R25, R27, R28 RESCAV-47K0-0W125-5T00-2N resistor, 4.7K, 1/8W, 1206x2 Concave R26, R32 RES-4K70-0805-1T00 resistor, 4.7K, 0805, 1% 1 R59 RES-4K70-0805-1T00 resistor, 4.7K, 0805, 1% 1 S1 SW_Panasonic_EVQ-PAE04M pushbutton 1 U1 IC_ATMEL_ATmega644P-20PU ATmega644P-20PU, 64K/4K/2K, 20MHz 1 U4 VREG_On-Semi_MC33269T-3.3G voltage regulator, 3.3V, 800mA, TO-220 1 U10 FTDL_FT232RL 1 U21 IC_DAC_TLTLV5618 IC, DAC, TLV5618, 2ch, 12bit, DIP-8 1 U22 IC_REF_LM4041AIZ-1.2 IC, REF, 1.225V, 0.1%, TO-92                                                                                                                                                                                                                                                                                                                                                 | 1   | F1              | $FUSE\_Littelfuse\_1812L050PR$ | fuse, 0.5A 1812                             |

| 2 J3, J9 HDR_BR-3X1-100M header, 3x1, 100mils 1 J6 HDR_BR-3X2-100M header, 3x2, 100mils 1 J10 CON_CUI-PJ-202AH power jack, 2.1mm 1 J60 Molex_67503-1020 1 L1 INDA-10UH-130M-10T0 inductor, 10uH, 10% 1 Q24 FET_P_On-Semi_NTR4101PT1G FET, P, -20V, 3.2A 1 R1 RES-10K0-0W25-1T00 resistor, 10K, 1/4W, 1% 1 R2 RES-374R-0W125-1T00 resistor, 374 Ohm, 1/8W, 1% 1 R21 RES-2K10-0W125-1T00 resistor, 2.1K, 1/8W, 1% 2 R22, R23 RES-4K70-0W125-1T00 resistor, 4.7K, 1/8W, 1% 3 R24, R58, R62 RES-10K0-0805-1T00 resistor, 10K, 0805. 1% 3 R25, R27, R28 RESCAV-47K0-0W125-5T00-2N resistor, 4.7K, 1/8W, 1206x2 Concave R26, R32 RES-4K70-0805-1T00 resistor, 4.7K, 0805, 1% 1 R59 RES-4K70-0805-1T00 resistor, 4.7K, 0805, 1% 1 S1 SW_Panasonic_EVQ-PAE04M pushbutton 1 U1 IC_ATMEL_ATmega644P-20PU ATmega644P-20PU, 64K/4K/2K, 20MHz 1 U4 VREG_On-Semi_MC33269T-3.3G voltage regulator, 3.3V, 800mA, TO-220 1 U10 FTDL_FT232RL 1 U21 IC_DAC_TLTLV5618 IC, DAC, TLV5618, 2ch, 12bit, DIP-8 1 U22 IC_REF_LM4041AIZ-1.2 IC, REF, 1.225V, 0.1%, TO-92                                                                                                                                                                                                                                                                                                                                                 | 1   | J1              | HDR_RA_BR-17X2-100M            | header, RA, 17x2, 100mils                   |

| 1       J6       HDR_BR-3X2-100M       header, 3x2, 100mils         1       J10       CON_CUI-PJ-202AH       power jack, 2.1mm         1       J60       Molex_67503-1020         1       L1       INDA-10UH-130M-10T0       inductor, 10uH, 10%         1       Q24       FET_P_On-Semi_NTR4101PT1G       FET, P, -20V, 3.2A         1       R1       RES-10K0-0W25-1T00       resistor, 10K, 1/4W, 1%         1       R2       RES-374R-0W125-1T00       resistor, 374 Ohm, 1/8W, 1%         1       R21       RES-2K10-0W125-1T00       resistor, 2.1K, 1/8W, 1%         2       R22, R23       RES-4K70-0W125-1T00       resistor, 10K, 0805. 1%         3       R24, R58, R62       RES-10K0-0805-1T00       resistor, 10K, 0805. 1%         3       R25, R27, R28       RESCAV-47K0-0W125-5T00-2N       resistor network, 47K, 1/8W, 1206x2 Concave         2       R26, R32       RES-4K70-0805-1T00       resistor, 4.7K, 0805, 1%         1       R59       RES-4K70-0805-1T00       resistor, 4.7K, 0805, 1%         1       V1       IC_ATMEL_ATmega644P-20PU       ATmega644P-20PU, 64K/4K/2K, 20MHz         1       U4       VREG_On-Semi_MC33269T-3.3G       voltage regulator, 3.3V, 800mA, TO-220         1       U10       FTDLFT232RL <th>2</th> <td>J3, J9</td> <td>HDR_BR-3X1-100M</td> <td></td>                                                                         | 2   | J3, J9          | HDR_BR-3X1-100M                |                                             |

| 1       J10       CON_CUI-PJ-202AH       power jack, 2.1mm         1       J60       Molex_67503-1020         1       L1       INDA-10UH-130M-10T0       inductor, 10uH, 10%         1       Q24       FET_P_On-Semi_NTR4101PT1G       FET, P, -20V, 3.2A         1       R1       RES-10K0-0W25-1T00       resistor, 10K, 1/4W, 1%         1       R2       RES-374R-0W125-1T00       resistor, 374 Ohm, 1/8W, 1%         1       R21       RES-2K10-0W125-1T00       resistor, 2.1K, 1/8W, 1%         2       R22, R23       RES-4K70-0W125-1T00       resistor, 4.7K, 1/8W, 1%         3       R24, R58, R62       RES-10K0-0W125-5T00-2N       resistor, 10K, 0805. 1%         3       R25, R27, R28       RESCAV-47K0-0W125-5T00-2N       resistor network, 47K, 1/8W, 1206x2 Concave resistor, 47.5K, 0805, 1%         2       R26, R32       RES-4K70-0805-1T00       resistor, 4.7K, 0805, 1%         1       R59       RES-4K70-0805-1T00       resistor, 4.7K, 0805, 1%         1       SW_Panasonic_EVQ-PAE04M       pushbutton         1       U1       IC_ATMEL_ATmega644P-20PU       ATmega644P-20PU, 64K/4K/2K, 20MHz         1       U4       VREG_On-Semi_MC33269T-3.3G       voltage regulator, 3.3V, 800mA, TO-220         1       U10       FTDL                                                                                                                          | 1   |                 | HDR_BR-3X2-100M                | header, 3x2, 100mils                        |

| 1         L1         INDA-10UH-130M-10T0         inductor, 10uH, 10%           1         Q24         FET_P_On-Semi_NTR4101PT1G         FET, P, -20V, 3.2A           1         R1         RES-10K0-0W25-1T00         resistor, 10K, 1/4W, 1%           1         R2         RES-374R-0W125-1T00         resistor, 374 Ohm, 1/8W, 1%           1         R21         RES-2K10-0W125-1T00         resistor, 2.1K, 1/8W, 1%           2         R22, R23         RES-4K70-0W125-1T00         resistor, 4.7K, 1/8W, 1%           3         R24, R58, R62         RES-10K0-0805-1T00         resistor, 10K, 0805. 1%           3         R25, R27, R28         RESCAV-47K0-0W125-5T00-2N         resistor network, 47K, 1/8W, 1206x2 Concave           2         R26, R32         RES-4K70-0805-1T00         resistor, 47.5K, 0805, 1%           1         R59         RES-4K70-0805-1T00         resistor, 4.7K, 0805, 1%           1         S1         SW_Panasonic_EVQ-PAE04M         pushbutton           1         U1         IC_ATMEL_ATmega644P-20PU         ATmega644P-20PU, 64K/4K/2K, 20MHz           1         U4         VREG_On-Semi_MC33269T-3.3G         voltage regulator, 3.3V, 800mA, TO-220           1         U10         FTDLFT232RL         IC, DAC, TLV5618, 2ch, 12bit, DIP-8           1         U2                                                                      | 1   | J10             | CON_CUI-PJ-202AH               |                                             |

| 1         Q24         FET.POn-Semi.NTR4101PT1G         FET, P, -20V, 3.2A           1         R1         RES-10K0-0W25-1T00         resistor, 10K, 1/4W, 1%           1         R2         RES-374R-0W125-1T00         resistor, 374 Ohm, 1/8W, 1%           1         R21         RES-2K10-0W125-1T00         resistor, 2.1K, 1/8W, 1%           2         R22, R23         RES-4K70-0W125-1T00         resistor, 4.7K, 1/8W, 1%           3         R24, R58, R62         RES-10K0-0805-1T00         resistor, 10K, 0805. 1%           3         R25, R27, R28         RESCAV-47K0-0W125-5T00-2N         resistor network, 47K, 1/8W, 1206x2 Concave           2         R26, R32         RES-4K70-0805-1T00         resistor, 4.7K, 0805, 1%           1         R59         RES-4K70-0805-1T00         resistor, 4.7K, 0805, 1%           1         SW_Panasonic_EVQ-PAE04M         pushbutton           1         U1         IC_ATMEL_ATmega644P-20PU         ATmega644P-20PU, 64K/4K/2K, 20MHz           1         U4         VREG_On-Semi_MC33269T-3.3G         voltage regulator, 3.3V, 800mA, TO-220           1         U10         FTDI_FT232RL         IC, DAC, TLV5618, 2ch, 12bit, DIP-8           1         U22         IC_REF_LM4041AIZ-1.2         IC, REF, 1.225V, 0.1%, TO-92                                                                                              | 1   | J60             | Molex_67503-1020               | • ,                                         |

| 1         Q24         FET.POn-Semi.NTR4101PT1G         FET, P, -20V, 3.2A           1         R1         RES-10K0-0W25-1T00         resistor, 10K, 1/4W, 1%           1         R2         RES-374R-0W125-1T00         resistor, 374 Ohm, 1/8W, 1%           1         R21         RES-2K10-0W125-1T00         resistor, 2.1K, 1/8W, 1%           2         R22, R23         RES-4K70-0W125-1T00         resistor, 4.7K, 1/8W, 1%           3         R24, R58, R62         RES-10K0-0805-1T00         resistor, 10K, 0805. 1%           3         R25, R27, R28         RESCAV-47K0-0W125-5T00-2N         resistor network, 47K, 1/8W, 1206x2 Concave           2         R26, R32         RES-4K70-0805-1T00         resistor, 4.75K, 0805, 1%           1         R59         RES-4K70-0805-1T00         resistor, 4.7K, 0805, 1%           1         SW_Panasonic_EVQ-PAE04M         pushbutton           1         U1         IC_ATMEL_ATmega644P-20PU         ATmega644P-20PU, 64K/4K/2K, 20MHz           1         U4         VREG_On-Semi_MC33269T-3.3G         voltage regulator, 3.3V, 800mA, TO-220           1         U10         FTDI_FT232RL         IC, DAC, TLV5618, 2ch, 12bit, DIP-8           1         U22         IC_REF_LM4041AIZ-1.2         IC, REF, 1.225V, 0.1%, TO-92                                                                                             | 1   | L1              | INDA-10UH-130M-10T0            | inductor, 10uH, 10%                         |

| 1       R1       RES-10K0-0W25-1T00       resistor, 10K, 1/4W, 1%         1       R2       RES-374R-0W125-1T00       resistor, 374 Ohm, 1/8W, 1%         1       R21       RES-2K10-0W125-1T00       resistor, 2.1K, 1/8W, 1%         2       R22, R23       RES-4K70-0W125-1T00       resistor, 4.7K, 1/8W, 1%         3       R24, R58, R62       RES-10K0-0805-1T00       resistor, 10K, 0805. 1%         3       R25, R27, R28       RESCAV-47K0-0W125-5T00-2N       resistor network, 47K, 1/8W, 1206x2 Concave         2       R26, R32       RES-4K76-0805-1T00       resistor, 4.7K, 0805, 1%         1       R59       RES-4K70-0805-1T00       resistor, 4.7K, 0805, 1%         1       S1       SW_Panasonic_EVQ-PAE04M       pushbutton         1       U1       IC_ATMEL_ATmega644P-20PU       ATmega644P-20PU, 64K/4K/2K, 20MHz         1       U4       VREG_On-Semi_MC33269T-3.3G       voltage regulator, 3.3V, 800mA, TO-220         1       U10       FTDLFT232RL       IC, DAC, TLV5618, 2ch, 12bit, DIP-8         1       U22       IC_REF_LM4041AIZ-1.2       IC, REF, 1.225V, 0.1%, TO-92                                                                                                                                                                                                                                                                              | 1   | Q24             | FET_P_On-Semi_NTR4101PT1G      |                                             |

| 1       R2       RES-374R-0W125-1T00       resistor, 374 Ohm, 1/8W, 1%         1       R21       RES-2K10-0W125-1T00       resistor, 2.1K, 1/8W, 1%         2       R22, R23       RES-4K70-0W125-1T00       resistor, 4.7K, 1/8W, 1%         3       R24, R58, R62       RES-10K0-0805-1T00       resistor, 10K, 0805. 1%         3       R25, R27, R28       RESCAV-47K0-0W125-5T00-2N       resistor network, 47K, 1/8W, 1206x2 Concave resistor, 47.5K, 0805, 1%         1       R59       RES-4K70-0805-1T00       resistor, 4.7K, 0805, 1%         1       S1       SWPanasonic_EVQ-PAE04M       pushbutton         1       U1       IC_ATMEL_ATmega644P-20PU       ATmega644P-20PU, 64K/4K/2K, 20MHz         1       U4       VREGOn-Semi_MC33269T-3.3G       voltage regulator, 3.3V, 800mA, TO-220         1       U10       FTDLFT232RL       IC, DAC, TLV5618, 2ch, 12bit, DIP-8         1       U21       IC_DACTLTLV5618       IC, REF, 1.225V, 0.1%, TO-92                                                                                                                                                                                                                                                                                                                                                                                                                      | 1   |                 | RES-10K0-0W25-1T00             | resistor, 10K, 1/4W, 1%                     |

| 1       R21       RES-2K10-0W125-1T00       resistor, 2.1K, 1/8W, 1%         2       R22, R23       RES-4K70-0W125-1T00       resistor, 4.7K, 1/8W, 1%         3       R24, R58, R62       RES-10K0-0805-1T00       resistor, 10K, 0805. 1%         3       R25, R27, R28       RESCAV-47K0-0W125-5T00-2N       resistor network, 47K, 1/8W, 1206x2 Concave         2       R26, R32       RES-4K70-0805-1T00       resistor, 47.5K, 0805, 1%         1       R59       RES-4K70-0805-1T00       resistor, 4.7K, 0805, 1%         1       S1       SW_Panasonic_EVQ-PAE04M       pushbutton         1       U1       IC_ATMEL_ATmega644P-20PU       ATmega644P-20PU, 64K/4K/2K, 20MHz         1       U4       VREG_On-Semi_MC33269T-3.3G       voltage regulator, 3.3V, 800mA, TO-220         1       U10       FTDL_FT232RL       IC, DAC, TLV5618, 2ch, 12bit, DIP-8         1       U21       IC_REF_LM4041AIZ-1.2       IC, REF, 1.225V, 0.1%, TO-92                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1   | R2              | RES-374R-0W125-1T00            |                                             |

| 3 R24, R58, R62 RES-10K0-0805-1T00 resistor, 10K, 0805. 1% 3 R25, R27, R28 RESCAV-47K0-0W125-5T00-2N resistor network, 47K, 1/8W, 1206x2 Concave resistor, 47.5K, 0805, 1% 1 R59 RES-4K70-0805-1T00 resistor, 47.5K, 0805, 1% 1 S1 SW_Panasonic_EVQ-PAE04M pushbutton 1 U1 IC_ATMEL_ATmega644P-20PU ATmega644P-20PU, 64K/4K/2K, 20MHz 1 U4 VREG_On-Semi_MC33269T-3.3G voltage regulator, 3.3V, 800mA, TO-220 1 U10 FTDL_FT232RL 1 U21 IC_DAC_TL_TLV5618 IC, DAC, TLV5618, 2ch, 12bit, DIP-8 1 U22 IC_REF_LM4041AIZ-1.2 IC, REF, 1.225V, 0.1%, TO-92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1   | R21             | RES-2K10-0W125-1T00            | resistor, 2.1K, 1/8W, 1%                    |

| 3       R25, R27, R28       RESCAV-47K0-0W125-5T00-2N       resistor network, 47K, 1/8W, 1206x2 Concave         2       R26, R32       RES-47K5-0805-1T00       resistor, 47.5K, 0805, 1%         1       R59       RES-4K70-0805-1T00       resistor, 4.7K, 0805, 1%         1       S1       SW_Panasonic_EVQ-PAE04M       pushbutton         1       U1       IC_ATMEL_ATmega644P-20PU       ATmega644P-20PU, 64K/4K/2K, 20MHz         1       U4       VREG_On-Semi_MC33269T-3.3G       voltage regulator, 3.3V, 800mA, TO-220         1       U10       FTDLFT232RL         1       U21       IC_DAC_TLV5618       IC, DAC, TLV5618, 2ch, 12bit, DIP-8         1       U22       IC_REF_LM4041AIZ-1.2       IC, REF, 1.225V, 0.1%, TO-92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2   | R22, R23        | RES-4K70-0W125-1T00            | resistor, 4.7K, 1/8W, 1%                    |

| 2 R26, R32 RES-47K5-0805-1T00 resistor, 47.5K, 0805, 1% 1 R59 RES-4K70-0805-1T00 resistor, 4.7K, 0805, 1% 1 S1 SW_Panasonic_EVQ-PAE04M pushbutton 1 U1 IC_ATMEL_ATmega644P-20PU ATmega644P-20PU, 64K/4K/2K, 20MHz 1 U4 VREG_On-Semi_MC33269T-3.3G voltage regulator, 3.3V, 800mA, TO-220 1 U10 FTDI_FT232RL 1 U21 IC_DAC_TI_TLV5618 IC, DAC, TLV5618, 2ch, 12bit, DIP-8 1 U22 IC_REF_LM4041AIZ-1.2 IC, REF, 1.225V, 0.1%, TO-92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3   | R24, R58, R62   | RES-10K0-0805-1T00             | resistor, 10K, 0805. 1%                     |

| 1       R59       RES-4K70-0805-1T00       resistor, 4.7K, 0805, 1%         1       S1       SW_Panasonic_EVQ-PAE04M       pushbutton         1       U1       IC_ATMEL_ATmega644P-20PU       ATmega644P-20PU, 64K/4K/2K, 20MHz         1       U4       VREG_On-Semi_MC33269T-3.3G       voltage regulator, 3.3V, 800mA, TO-220         1       U10       FTDLFT232RL         1       U21       IC_DAC_TLV5618       IC, DAC, TLV5618, 2ch, 12bit, DIP-8         1       U22       IC_REF_LM4041AIZ-1.2       IC, REF, 1.225V, 0.1%, TO-92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3   | R25, R27, R28   | RESCAV-47K0-0W125-5T00-2N      | resistor network, 47K, 1/8W, 1206x2 Concave |

| 1       S1       SW_Panasonic_EVQ-PAE04M       pushbutton         1       U1       IC_ATMEL_ATmega644P-20PU       ATmega644P-20PU, 64K/4K/2K, 20MHz         1       U4       VREG_On-Semi_MC33269T-3.3G       voltage regulator, 3.3V, 800mA, TO-220         1       U10       FTDL_FT232RL         1       U21       IC_DAC_TLTLTLV5618       IC, DAC, TLV5618, 2ch, 12bit, DIP-8         1       U22       IC_REF_LM4041AIZ-1.2       IC, REF, 1.225V, 0.1%, TO-92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2   | R26, R32        | RES-47K5-0805-1T00             | resistor, 47.5K, 0805, 1%                   |

| 1       S1       SW_Panasonic_EVQ-PAE04M       pushbutton         1       U1       IC_ATMEL_ATmega644P-20PU       ATmega644P-20PU, 64K/4K/2K, 20MHz         1       U4       VREG_On-Semi_MC33269T-3.3G       voltage regulator, 3.3V, 800mA, TO-220         1       U10       FTDL_FT232RL         1       U21       IC_DAC_TLTLTLV5618       IC, DAC, TLV5618, 2ch, 12bit, DIP-8         1       U22       IC_REF_LM4041AIZ-1.2       IC, REF, 1.225V, 0.1%, TO-92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1   | R59             | RES-4K70-0805-1T00             | resistor, 4.7K, 0805, 1%                    |

| 1       U4       VREG_On-Semi_MC33269T-3.3G       voltage regulator, 3.3V, 800mA, TO-220         1       U10       FTDLFT232RL         1       U21       IC_DAC_TLTLTLV5618       IC, DAC, TLV5618, 2ch, 12bit, DIP-8         1       U22       IC_REF_LM4041AIZ-1.2       IC, REF, 1.225V, 0.1%, TO-92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1   | S1              | SW_Panasonic_EVQ-PAE04M        |                                             |

| 1 U10 FTDLFT232RL<br>1 U21 IC_DACTLTLV5618 IC, DAC, TLV5618, 2ch, 12bit, DIP-8<br>1 U22 IC_REFLM4041AIZ-1.2 IC, REF, 1.225V, 0.1%, TO-92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1   | U1              | $IC\_ATMEL\_ATmega644P-20PU$   | ATmega644P-20PU, 64K/4K/2K, 20MHz           |

| 1 U21 IC_DACTI_TLV5618 IC, DAC, TLV5618, 2ch, 12bit, DIP-8<br>1 U22 IC_REFLM4041AIZ-1.2 IC, REF, 1.225V, 0.1%, TO-92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1   | U4              | $VREG\_On-Semi\_MC33269T-3.3G$ | voltage regulator, 3.3V, 800mA, TO-220      |

| 1 U22 IC_REFLM4041AIZ-1.2 IC, REF, 1.225V, 0.1%, TO-92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1   | U10             | FTDLFT232RL                    |                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1   | U21             | IC_DACTI_TLV5618               | IC, DAC, TLV5618, 2ch, 12bit, DIP-8         |

| 1 U23 IC_RTCMaxim_DS1337+ IC, RTC, DS1377+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1   | U22             | IC_REFLM4041AIZ-1.2            | IC, REF, 1.225V, 0.1%, TO-92                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1   | U23             | $IC_RTC_Maxim_DS1337+$         | IC, RTC, DS1377+                            |

| 1 U24 Molex_502702-0891                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1   | U24             | $Molex_502702-0891$            |                                             |

| $1  \text{U55} \qquad \qquad \text{TLSN65220DBV}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1   | U55             | $TI_SN65220DBV$                |                                             |

| 1 X1 XTAL-12M-20P-HC49US crystal, 12MHz, 20pF, HC49US                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1   | X1              | XTAL-12M-20P-HC49US            | crystal, 12MHz, 20pF, HC49US                |